����ժҪ�������һ�־��п���ʽ�ܹ������������ݴ����ն�ƽ̨������RapidIO��Ϊ�������忨�ļ��ָ��ӿڣ�������8×PCIe��Ϊ�������忨�����ݽӿڡ��������Դ�������米��ʵ��ϵͳ�����������ͨ�ô����忨ͨ�������ع���ʵ���������е��ƻ��������н��չ��ܣ����н��յ�����ͨ�������ݴ��䣬����������ߴ�40 Gb/s;ͨ��������������������չ��̬������ʵ�����ݸ��ټ�¼�����ݼ�¼���ʲ�����500 MB/s;ͨ��������̫���ӿ�ʵ�����ݸ���ʵʱת��������ת�����ʲ�����4 Gb/s;���е�������ʵʱע��ʵʱ���ƣ��������ʲ�����2 Gb/s.��ƽ̨Ӳ������չ�����������������ƺ��������߽���ϣ���ͨ�������ع�ʵ�ֹ������ú����߸��£��������õ���չ�Ժ�ͨ���ԣ����ڵ����ն�վ�������ݴ���ϵͳ�еõ�����Ӧ�á�

�����ؼ��������ǵ���վ�� �������ݴ����նˣ� �����ع��� ����ʽ�ܹ���

����Abstract:A new high speed data transceiver platform with open architecture is provided in which serial RapidIO is performed as control and command interface and PCIe with two 8 lanes is performed as data interface.Data exchange is realized through active switching network backplane.The common processing board is designed to realize modulation or data receiving function by software reconstruction.The data received in the downlink can be transmitted through block data with transmission rate up to 40 Gb/s.High-speed data recording can be realized through redundant array independent disk��RAID�� extended solid-state disk��SSD�� array with data recording rate to 500 MB/s.Data can also be transmitted through 10 GbE��Gigabit Ethernet�� interface with data rate to 4 Gb/s.Modulation data is injected and modulated in real-time with rate to 2 Gb/s.The platform can be expanded in hardware,upgraded in software,decoupled in control and data bus,and function programme and online update can be realized through software reconfiguration.It has good scalability and versatility.It has been successfully applied in ground terminal station high speed data transmission system.

����Keyword:satellite ground station; high speed data transceiver; software reconfiguration; open architecture;

����0 �� ��

���������������Ÿ�������ͨ��Ӧ������IJ�����չ���ر�������졢�м̡���Դ̽�⡢�߷ֱ��ʶԵع۲�������У������������ߴ��似��Ӧ����Խ��Խ�㷺������Ϊ�����������ߴ���ϵͳ�еĵ����ն��豸��Ҫ�Խӵ���������Խ��Խ�֧࣬�����ݵ��ƽ����ʽ���ֶ��������ݴ������Խ��Խ��������������Խ��Խ�࣬��Ҳ��Ϊ���������ݴ����ն˱�Ȼ��ԵĹ�������

������ͳ�������ݴ����ն˵������ܹ������¼��ַ�ʽ��һ�Dz������õ���Χ���������Peripheral Component Interconnect,PCI������Χ��չ���������Peripheral Component Interconnect Express,PCIe���������ھ���PCI[1]��PCIe[2]�ӿڵķ����������������ƹ��ܿ���ÿ�������һ���ֶ�������[3],�編��In-snec��˾�ṩ����ز�Ʒ���Ǵ��ּܹ������ּܹ����ŵ�������Ϊ�����ò�Ʒ�����ֻ���ص��עPCI/PCIe���ܿ�����ƣ�ȱ���ǹ��ܿ�û����չ������ÿһ�����ܿ����������ܿ�֮���ͨ��Ҫôͨ���忨��ĸ��ٷ��߽����Ҫôͨ��PCI��PCIe���߽��У���CPU�����˶���ĸ��������Dz��ý�����Χ���������Compact Peripheral Component Interconnect,CPCI����VPX�ܹ����ػ��������϶��ƿ������ܰ忨�������һЩ��У�Ϳ���Ժ���ṩ����ز�Ʒ�����˴˼ܹ���CPCI��VPXΪ���ܹ���Ҳ���㹻����Զ���ܽš�CPCI���еͳɱ��ص�[4,5],����û�и��ٴ�����·���������㴫����������ij��ϣ�VPX���зḻ�ĸ��ٴ�����·[6],��VPX���䶯����10����ۼ�Ҳ���������ƹ㣬�Ҷ���4U�߶ȵ��ϼ��豸��VPXֻ���ṩ6����λ����ȥϵͳ�������Ƶ�ŵ����ռ�ݵIJ�λ�⣬���Զ���IJ�λֻ��4������Ҫʹ�ø���Ĺ��ܰ忨��Ҫ���ӻ���߶ȣ��������豸������۵���ƺ������Ŀ��ơ����⣬���Ÿ����ǵ�ͨ�����ʵIJ�����������ʵ��ʹ���з��ָ��ٿ�������ͨ�Ź����п���ָ����Ӧ����ʱ������ҲԽ��Խͻ����

������ˣ�������Դ�ͳ�ն˾��е����⣬��Ƴ���һ�־��п���ʽ�ܹ���Ӳ������չ�����������������ƺ��������߽���ϣ����豸�ɱ��ɿص����������ݴ����ն�ƽ̨��

����1 ϵͳ�ܹ�����

�������������һ�־��п���ʽ�ܹ���֧�ְ忨Ӳ�����������ܿ��ع���������������չ�ĸ������ݴ����ն�ƽ̨��������PCIe��RapidIO����˫�������ߣ��������״̬��Ϣͨ��4×���ٴ���RapidIO���д��䣬���ɸ������忨�ϵ����ִ�������Digital Signal Processer,DSP��������������Ҫ������������Ŀ�����ͨ��8×����PCIe�ӿڽ��д��䣬���ɸ������忨�ϵĿɱ���������У�Field Programmable Gate Array,FPGA��������ͨ�����ַ�ʽʵ����ϵͳ�Ŀ�������ʹ������ݽ���ϣ������˸�оƬ�Ĵ���ѹ���������ϵͳʵʱ��Ӧ�����Ϳɿ��ԡ�

����ͬʱ�����ն˾��п���ʽ�ص㡣���ñ����źŶ��壬���ڽ��Ӳ���忨�������ԭλ����������Ͽ��ǵ����ֵ��ƽ����ʽ�����ֱ�����ȵ������ԣ���FPGA��DSP������֧�����߿��ع���֧�ֳ������߸��£��Ա�֤�豸�Ŀ�ά���ԺͿ������������������õ���չ�ԡ�

�����������ݴ����ն�ƽ̨��Ƶ���Ҫ˼��ɸ���Ϊ���������ߺͿ������߷��룬�����³���ԣ�����֧�ֶ�Ķ�������ͨ�����������չ�ԣ�����֧��������չ�����Խ��ͳɱ���

���������������˼·��������Ƶ��ն�ϵͳ���߲����˸��ٴ���PCIe��RapidIO˫�������ߣ��ɸ����û��������ö��������Ԫ�����ж����PCIe��չ��λ����֧�����û��ܽӿڰ忨�����У�RapidIO֧��2.1�淶��ͨ������Ϊ4 lanes 3.125 Gb/s,���֧��6.25 Gb/s;PCIe��ѭ3.0�淶��ͨ������Ϊ8ͨ��8 Gb/s,����PCIe�ӿڴ����ɴ�40 Gb/s,�������㳣�ô����忨�ӿ����ʵĴ���Ҫ��

����ͨ�ô����忨ͨ������DSP+FPGA�Ľṹ��ʹ��DSP����RapidIO�ӿ���Ϊ�忨����ع�������оƬ��ʹ��FPGA����PCIe�ӿ����ڴ��������Ŀ����ݵķ��ͺͽ��ա�ͨ�ô����忨ͨ�������ع������ó�Ϊ�������е��Ƶ�Ԫ��Ҳ�������ó�Ϊ�������н��յ�Ԫ�����У��������е��Ƶ�Ԫ���տ�������������ע�벢���ƣ��������н��յ�Ԫ�����յ��Ŀ����������ϵͳ������д洢��ͨ����ؽӿڿɷ��ͳ������߸���ָ��Ը��忨�ϸ�FPGA��DSP��Ԫ���г�����¡����⣬ͨ��DSP�Ͱ��Ϲ̼���Ϲ�������ʵ�ְ忨�Ŀ��ع���ʵ�ֿ����������ն��豸������ҪӲ���������ɽ����Ϲ淶����İ忨����Ԥ���IJ�λ�����Ӳ����������

��������ͨ��PCIe��λ������չ֧�־���×8�ӿڵı����õĽӿڿ�����������̫���������������������У�Redundant Array Independent Disk,RAID�����ƿ���������չ���ȣ���ʵ�ֶ���ӿڵ���չ��

��������4U 19����1��=2.54���ף����ϼܽṹ��VPX���ػ���˵�����ڽṹ�ߴ����ƣ�ֻ�ܲ���4���Զ���忨����������ƵĴ����ն���Ч������4U������ȵĿռ䣬��4U�߶��пɲ���2��ͨ��PCIe��չ����8��ͨ�ô����忨�����⣬ʹ�÷���PICMG 1.3���Ĺ�ҵ���������ṩ����ģ�鹦�ܣ����ṩWindows���������ϵͳ���˻��������档

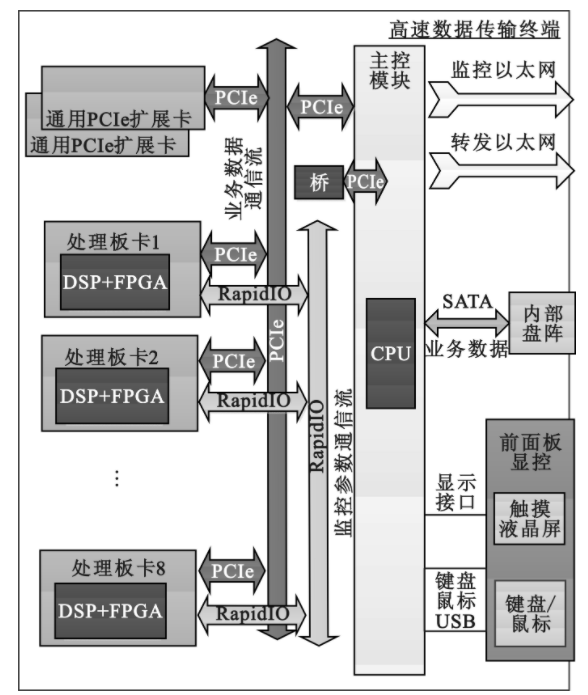

�����������ݴ����ն�ϵͳ�ܹ�������ͼ��ͼ1��ʾ��

����ͼ1 �������ݴ����ն�ϵͳ�ܹ���ͼ

����2 �ն����ʵ��

����2.1 �ն���Դ��������ʵ��

����Ϊ�˽�ʡ�忨�ռ䣬������IJ�λ���������忨��������һ��CPCI��VPXƽ̨������Դ������ӽ���ģ��ķ�ʽ�����Ľ��ն˵�PCIe+RapidIO�������繦�����ϵ���Դ�����ϣ��Ⱥ��������˱������ռ䣬��Ϊ���ܰ忨�����˸�����Զ����λ��

��������ѡ�û���PICMG 1.3�淶�����壬������1��16×PCIe 3.0�ӿں�1��4×PCIe 2.0�ӿڡ�

��������Դ���������PCIe����оƬ����չ1·4×PCIe 2.0�ӿڣ���ͨ��PCIeתRapidIO�Ž�оƬת��Ϊ4×5 Gb/s��RapidIO���ߣ������ͨ��RapidIO����оƬ��RapidIO�ӿ���չΪ����ӿڷֱ����ӵ������忨���Ӷ�ʵ���ն˿������ߵĽӿ���չ��ͨ��PCIe����оƬ������8×PCIe 3.0�ӿڷֱ����ӵ�����8��ͨ�����ֲ�λ��2����PCIe��չ��λ���Ӷ�ʵ���������ߵĽӿ���չ��

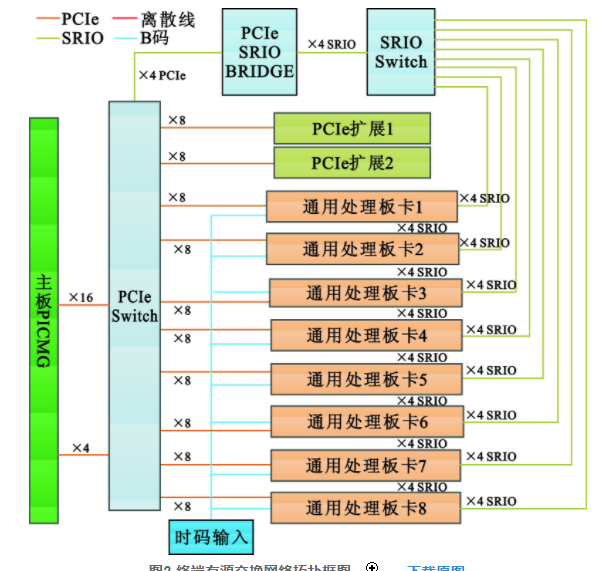

�����������ݴ����ն���Դ�����������˿�ͼ��ͼ2��ʾ��

����ͼ2 �ն���Դ�����������˿�ͼ

����2.2 ����ͨ�����ݽ���ʵ��

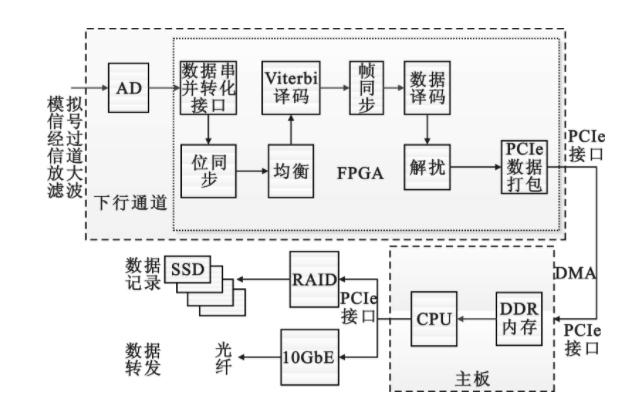

�����������ݴ����ն˽������Ǵ��������ĸ������ݣ�ͨ���������������ŵ����룬�����ݴ����ʵʱ������û�ʵ�ֺ���Դ���롢���ܵȡ�

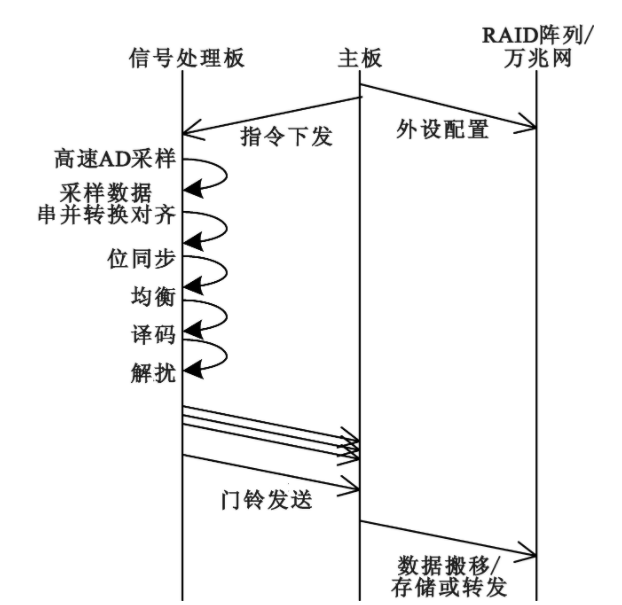

�����ź�����ͨ���ľ���ʵ�ֲ���Ϊ�����յ������źŷŴ��˲���ͨ������ģ��ת������Analog-to-Digital Converter,ADC���ɼ�����FPGA��ʵ�������±�Ƶ��λͬ�������⡢������������֡ͬ�������롢���ţ�Ȼ������ͨ��PCIe�ӿ���ֱ�Ӵ洢�����ʣ�Direct Memory Access,DMA����ʽ���뵽�����ڴ�[7],�������봦������Central Process Unit,CPU���������壻CPU���յ��������ڴ�ȡ���������ݿ������뵽�ն�����RAID��������[8]��ֱ��ͨ��������̫����ת�����ⲿ�洢��������

��������ͨ�����ݽ�������롢��¼��ת����������ͼ��ͼ3��ʾ��

����ͼ3 ����ͨ����������ͼ

�����ն�������������ͨ������ʵʱ��¼��ʵʩ����ת�����豸״̬��������ͼ��ͼ4��ʾ��

����ͼ4 ���չ���״̬��������ͼ

����2.3 ����ͨ�����ݵ���ʵ��

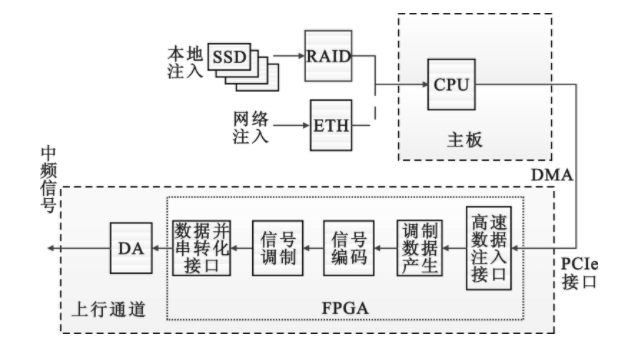

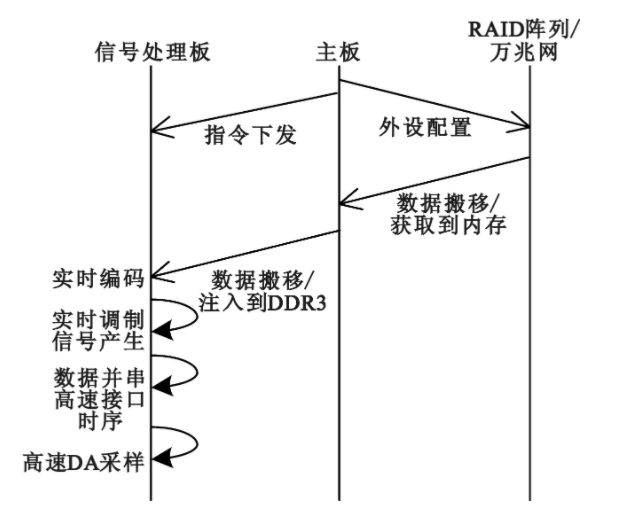

�����������ݴ����ն˽��û�����ͨ���ŵ����롢���Ƶ���Ƶ��ͨ��ǰ�˵��ƹ��š����ƣ�������ϵͳ�ϴ������ǡ�

�����ź�����ͨ���ľ���ʵ�ֲ���Ϊ���û�����ͨ����̫����ͨ�����ش洢�ļ�ע�룬ͨ��PCIe�ӿڵ�DMA��ʽע�뵽����ģ�飻FPGA��ע������ͨ����������ʵʱ�����������ʵʱ���ƣ�ͬʱ��ϸ�����ģת������Digital-to-Analog Converter,DAC��оƬֱ�����ɱ�����ƺ����Ƶģ���źţ��ٽ��ź�������ŵ���Ƶ�Ŵ��䣬��ͼ5��ʾ��

����ͼ5 ����ͨ��������ͼ

�����ն���������������������ע���ͨ��ʵʩ���롢���ơ�������豸״̬��������ͼ��ͼ6��ʾ��

����ͼ6 ���乤��״̬��������ͼ

����3 ��֤�Ͳ���

�����Ա�������ĸ������ݴ����ն�ƽ̨������֤�Ͳ��Ե���Ҫָ������������ߴ����������ԡ����ݼ�¼�������ԡ�����ע���������ԡ�

����3.1 ���ٱ������ߴ���ָ�����

����ʹ��WINNET��˾PCIeר�ò�����iTL32403-LL��ÿ����۵�PCIe���ߴ����������в��ԡ���8×5 Gb/s�������£�����������Ϊ1013,����ʱ�����30 min,��ͨ�������ʾ�Ϊ0,֤������ģ��ͨ�����ٱ���PCIe���ߴ��������ɴ�40 Gb/s.

����3.2 ������ݼ�¼��������

�������ն����ݼ�¼ʹ�û���Windows�ļ�ϵͳ�����ݼ�¼��ʹ��SSD Benchmark���߶��������ʽ��в��ԣ���8��RAID0�����£��������ж�д�����ʾ�����2 000 MB/s.

������ʵ�ʹ����У��������ݴ洢�Ǵ��ļ�ϵͳ�Ĵ洢��������洢Ч�ʽ��ͣ����չ���Ҫ���ն������˫·2 Gb/s�Ľ�����ݣ���4 Gb/s����ͨ������ͨ����ʵʱ��¼������ݣ�FPGA������˫ͨ������ͨ��PCIe DMA��������DDR3,�ټ�¼��SSD���У�ʵʱ��¼�����洢��������֤�����ݴ洢����������500 MB/s.

����3.3 ��������ע����������

�������ն˾�������ע�빦�ܣ����洢��SSD�����ϵĵ�������ͨ��PCIe����ע�뵽ͨ���źŴ������ϣ�����������ע�����ʲ�����1 GB/s��Ҫ��

������ʵ�ʹ���Ӧ���У�ʵʱ�������ݴ������Ϊ2 Gb/s,FIFO���ع��������������ݶ�ʧ�������֤������ʵʱע�롢ʵʱ��������������2 Gb/s.

������4������ת����������

�������ն˾�������ת�����������洢��SSD�����ϵĽ������ͨ��������̫���ӿ�ʵʱת�����ⲿ�豸��

������ʵ�ʹ����У��ն˽���˫·2 Gb/s�Ľ�����ݣ�������4 Gb/s����ͨ������ͨ��ʵʱ������ݣ�FPGA������˫ͨ������ͨ��PCIe DMA��������DDR3,��ͨ��������̫���ӿڿ�ת�����ⲿ��������������ת��������������֤������ʵʱת�����ʲ�����4 Gb/s.

����4 �� ��

�����봫ͳ�ĸ������ߴ����ն���ȣ���������Ļ��ڿ���ʽ�ܹ��ĸ������ݴ����ն�ƽ̨���еͳɱ��������ߡ�ͨ���ԡ�����������ܶȵ��ص㣬������������¼����棺

������1������VPX�Ȱ�����豸�ܹ�������ͨ���ػ������ϸĽ������������˳ɱ���

������2�����PCIe�������ߺ�RapidIO�������߷��룬����оƬ����ѹ���������ϵͳ³���ԡ�

������3��ʹ��ͨ���źŴ���ģ���ʵ�������������忨�ϵĶ�̬���úͲ��𣬰忨���ع����������������������õ���չ�ԡ�

������4������PCIe 3.0�������ߣ��忨�����ݴ�������ɴﵽ40 Gb/s.

������5�����ݼ�¼��ת�������ɴ�4 Gb/s,����ע�������ɴ�2 Gb/s.

������6����4U���ػ���С��ʵ��1�����塢8���Զ���忨��2����PCIe������·����ܶ���������չ��������

�����������������ڿ���ʽ�ܹ��ĸ������ݴ����ն�ƽ̨��Ϊ�����շ��նˣ��������ǵؼ伪���ظ����������ݴ��䡢��¼��ת�����������ڵ����ն�վ�������ݴ���ϵͳ�еõ�����Ӧ�ã���Ƕ��ʽ�������߿���ͨ�ŵ���������ƹ����塣

���������

����[1] ����������������������������PCI���ߵĸ������ݲɼ������[J].�������������ƣ�2012,20��12����3393-3396.

����[2] ��ľ������Ӱ������֮������PCIe���ߵĸ������ݲɼ��������ʵ��[J].��ؼ�����2013,32��7����19-22.

����[3] �����ڡ�����PCIE���ߵĸ������ݴ���ϵͳ�������ʵ��[D].�ɶ������ӿƼ���ѧ��2016.

����[4] ������������CPCI���ߵ�ͨ�ø����������ջ�[J].��Ѷ������2012,52��10����1644-1647.

����[5] ��褣�����ΰ��KSA�������ǻ�������ʵʱ�����ܹ������ʵ��[J].��Ѷ������2019,59��6����659-666.

����[6] ����ϼ����ʷ壬�ȡ�����TMS320C667x��VPX���״ﴦ��ϵͳ��Ƽ�Ӧ��[J].���ߵ繤�̣�2016,46��11����71-74.

����[7] �������ݣ���ΰ�����ȡ�����PCIE������ģʽDMA�������ݴ���ϵͳ���[J].���Ӽ���Ӧ�ã�2015,41��9����142-145.

����[8] WANG S M.PCIE interface design for high-speed image storage system based on SSD[C]//Proceedings of 2014 International Symposium on High Power Laser Systems and Applications.Chengdu:SPIE,2015:135-141.