摘要:介绍了Calibre验证技术和DRC验证的基本流程,并利用Calibre DRC平台自主设计检查金属密度及优化的验证规则文件来对版图进行优化,保证了版图在生产过程中不会由于金属分布不均而导致芯片失败。

关键词:集成电路; DRC验证; Calibre技术; 版图; 金属密度;

1 引言

在版图设计中重要。在集成电路芯片的版图的设计过程中,对于金属层存在着金属线资源分布不均匀的问题,这些在电路设计中是体现不出来的,但是在芯片的生产过程中,由于生产工艺的关系就会出现问题。在集成电路的生产中,金属密度不均匀会造成非常严重的安全隐患。利用Calibr DRC平台来自主设计检查金属密度及优化的验证规则文件来对版图进行优化。

2 集成电路版图验证流程

2.1 Calibre验证技术

Calibre是一套类似于Assura的验证软件,但其严谨度与可靠性远优于Assura,与Dracula相当[1].相对于Dracula优点:Dracula的操作比较复杂,且无法做在线验证。而Calibr不仅操作简易,更可搭配Virtuoso或其他layout软件做在线验证,所以Calibre在这些方面比Dracula技术稍有优势。

Calibre提供一套完整的工具满足大多数的验证要求:DRC来保证芯片在工艺上的正确性[2,3];LVS保证芯片的电连接正确[4];精确产生蒙板数据;打印输出,进行视觉上的查错。这些模块都是集成的,针对同一个数据,这样保证了每个IC验证流程的兼容性。

2.2 Calibre DRC验证技术

Calibre工具是基于Cadence平台上的一个版图验证工具,虽然Metor公司提供了这一套完整的验证工具以及DRC(设计规则检查)文件的命令格式,但要验证版图,必须要有与版图相匹配的DRC文件,这就要求版图设计人员根据集成电路的制造工艺来设计完整的DRC规则,DRC规则的编写首先要了解整个集成电路工艺的制造过程,还要掌握Calibre工具的命令格式。DRC规则文件的设计完成可以帮助设计人员对版图的正确性进行检查,以便完成后续的验证。所以DRC必不可少。

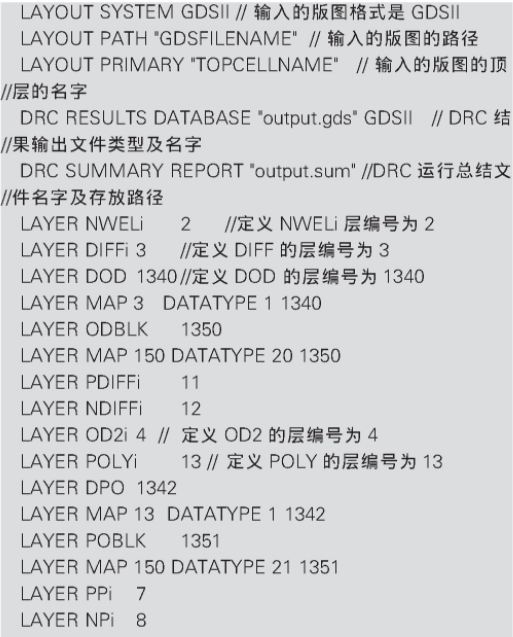

在版图设计完成后需要对版图进行设计规则检查(DRC),DRC检查的输入有两个,一个是已经完成的版图(一般为GDSII格式),另外一个是设计规则文件,一般由生产厂家提供,有时候也由设计者根据生产厂家的要求自行编写。通过验证工具生成的报告在版图界面上用各种不同的颜色标记定位错误,手工对错误进行修改,直到完全正确为止。

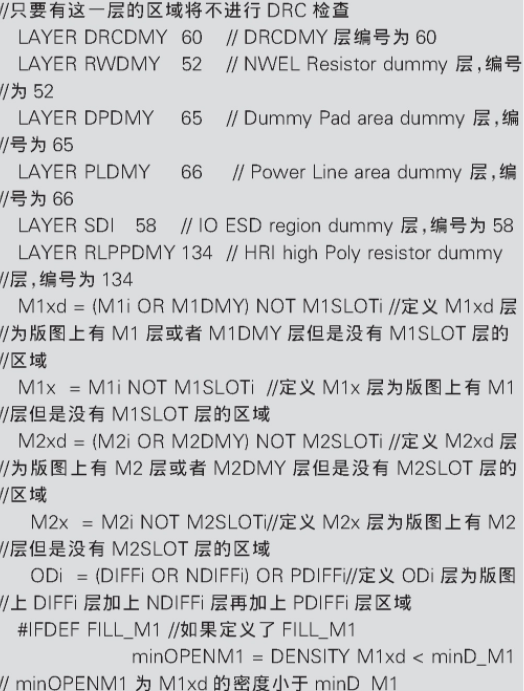

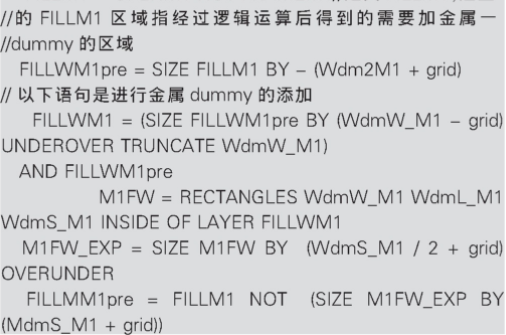

利用Calibre DRC验证工具对版图进行金属密度的检查以及自动优化。

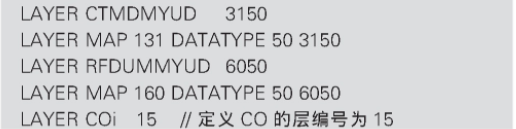

下面简单介绍下利用Calibre DRC工具自主设计的验证金属密度及优化的规则文件。

2.3 CALIBRE DRC验证实例

以与非门为示例对自主设计的验证规则文件作了测试。

(1)按照电路原理图绘制与非门的版图,与非门版图如图1所示。

(2)新建一个文件夹,名字叫"check",在这个文件夹下面建3个文件夹,名字分别为"DRC","rule"和"GDS".其中文件夹"rule"用来放DRC规则文件,"GDS"用来放版图提取出来的GDS文件,"DRC"则用来放DRC的结果文件;(3)导出GDS文件到文件夹"GDS"中;(4)打开Calibre DRC界面。(5)在Calibre DRC窗口选择规则文件和跑DRC的路径;(6)在Calibre DRC窗口输入GDS名称以及TOP CELL的名称;(7)点击"Rus DRC"来跑DRC.当DRC运行完毕,会有一个输出结果文件,这个输出结果文件进行倒入,会得到一个新的版图。把这个版图和原版图放在一起产生的新的版图,金属密度就符合要求了。

图1 与非门版图

3 结语

从上述版图的验证实例,可知利用Calibre DRC验证工具和自主设计的严正规则文件可以对版图的金属密度进行检查以及优化,操作界面主要为图形模式,图形模式可以单独启动又可以嵌入Virtuoso等软件,检查结果准确且完善。示例验证虽然使用0.18um工艺,但通过对验证规则文件的修改,也可以满足其他各种不同的工艺的版图的验证。在0.18um以下的设计中,充分利用该工具可以给版图设计工作带来很大的好处,减少版图设计工作人员的负担,大大缩短设计周期并得到精确稳定的结果。

参考文献

[1]于涛,窦刚谊。基于Calibre工具的So C芯片的物理验证[J].科学技术与工程,2007,(5):836-838.

[2]朱月珍。芯片版图设计优化技术研究[D].苏州:苏州大学,2014.

[3]胡心仪,林殷茵。版图邻近效应的高精度标准单元波动检测电路[J].半导体技术,2015,(10):754-758.

[4]王仁平,何明华,魏榕山。基于MCU的So C芯片版图设计与验证[J].福州大学学报(自然科学版),2011,(4):539-545.