摘要:设计了基于1T1R结构的16kb相变存储器(PCRAM)芯片及其版图。芯片包括存储阵列、外围读写控制电路、纠错电路(ECC)、静电防护电路(ESD)。版图上对纳米存储单元(1R)与CMOS工艺的融合作了优化处理,给出了提高存储单元操作电流热效率的具体方法。1R位于顶层金属(TM)和二层金属(TM-1)之间,包含存储材料以及上下电极,需要在传统CMOS工艺基础上添加掩膜版。读出放大器采用全对称的差分拓扑结构,大大提升了抗干扰能力、灵敏精度以及读出速度。针对模块布局、电源分配、二级效应等问题,给出了版图解决方案。采用中芯国际130nm CMOS工艺流片,测试结果显示芯片成品率(bit yield)可达99.7%.

关键词:相变存储器; 1T1R; 版图设计;

Abstract:A phase change random access memory(PCRAM)chip with 16 kb capacity based on 1T1 Rstructure was designed and verified.The chip consisted of memory array,write and read control circuits,error correcting code(ECC)circuits and ESD(electro-static discharge)protection circuits.Special handling and optimization was made on the layout to merge memory cell(1R)with the traditional CMOS process.Solutions were given to improve the thermal efficiency of cell operation current.1Rlayer located between the top metal(TM)and the second metal(TM-1),which was composed of memory materials,top and bottom electrode.Additional masks were needed to be added based on the traditional CMOS process.A fully symmetrical sense amplifier topology structure was adopted in read sense amplifier to improve the anti-inference ability,precision accuracy and read speed.Layout efforts in block floor plan,power distribution and second-order effects had been introduced in detail.It's taped out in the SMIC 130 nm CMOS process.Test results showed that the bit yield of the proposed PCRAM chip was up to 99.7%.

Keyword:PCRAM; 1T1R; Layout design;

1 引 言

存储器产品在集成电路市场中一直占据着较大的份额。作为主流非易失存储器的Flash是一种基于电荷存储的非 易失性存 储器,采用具有 浮栅的MOS管来存储电荷。随着集成电路工艺节点的缩小,Flash面临光刻极限以及可靠性的双重挑战,22nm工艺节点下,Flash浮栅内所能存储的电荷数量已减少到1 000个电子以下,使得这一技术的可靠性大大降低,其可反复操作次数也随之急剧下降[1].

在此背景下,业界加大了对新型存储技术的研发力度,包括磁存 储器 (Magnetic Random AccessMemory, MRAM )、电阻存储 器 (ResistanceRandom Access Memory,ReRAM)、铁电存储 器(Ferroelectric Random Access Memory,FeRAM)以及相变存 储器 (Phase Change Random AccessMemory,PCRAM)。

MRAM已推向市场的最大容量为64Mb,对复杂的3D垂直器件结构的挑战,以及降低功耗与提高高低磁阻比例的矛盾,限制了MRAM在大容量上的作为。FeRAM也面临容量限制问题,铁电材料在单元尺寸缩小至一定程度时会失去铁电效应,限制了其朝 高密度方 向的发展,目前报道 的FeRAM的最大存储容量为128 Mb.ReRAM的研究重点在器件制备以及存储机理方面,虽有相关芯片及操作参数的报道,但是芯片成品率以及工艺控制存在很大 问题,尚未有可 商用的成 熟芯片。PCRAM因具有与CMOS工艺兼容、存储单元可按比例缩小、高速、低功耗、掉电非易失和抗疲劳特性等诸多优点,被广为看好[2].

在容量方面,PCRAM芯片已有Gb量级的报道。相变材料的物理特性显示其工艺特征尺寸有望缩小到5nm节点以下[3].PCRAM的存储机理是基于硫系化合物材料(典型材料为Ge2Sb2Te5,GST),通过施加SET和RESET电流脉冲实现材料在低阻晶态和高阻非晶态之间的可逆相变[4],通过阻值的差异来表征二进制数据"0"和"1",实现存储功能。

为了把具有我国自主知识产权的该新兴存储技术尽快推向市场,中科院微系统所选择了市场应用广泛,而且具有 特殊功能 的SPI(Serial PeripheralInterface)接口的16kb PCRAM芯片作为突破方向之一。该芯片采用中芯国际130nm CMOS工艺设计并流片。文章详细介绍了该芯片核心存储单元的构成,解析了电路架构及版图实现,并给出了芯片的测试结果。

2 存储单元

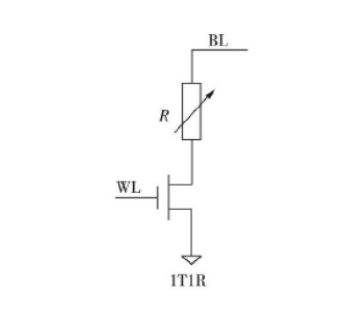

图1所示为存储单元的电路结构示意图,存储单元为垂直的1T1R结构,以NMOS晶体管(T)作为相变电阻(R)选通管的开关,NMOS管的源极接地,栅极连接字线(WL),相变电阻一端连接NMOS管漏极,另一端连接位线(BL)。

对选中存储单元进行操作时,对应单元的WL连接高电平,NMOS管打开;同时,读写驱动电路将电流脉冲施加到对应的BL上,实现对存储单元的读写操作。存储单元写"0"被称为RESET操作,施加高而窄的电流脉冲,将相变材料加热到熔化温度以上,形成高阻非晶态;写"1"被称为SET操作,施加低而宽的电流脉冲,将相变材料加热到结晶温度以上、熔化温度以下,使相变材料充分结晶,形成低阻多晶态。读操作时,对相变材料施加幅值较小、宽度适中的电流脉冲,通过测量相变材料电阻值的大小读出数据"0"或者"1".

图1 存储单元电路示意图

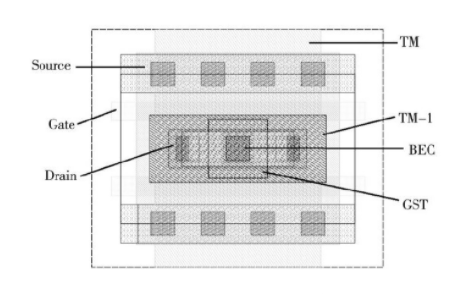

图2所示为存储单元的版图,NMOS采用折叠结构,共享漏极 (Drain),这样上下 相邻的两 个NMOS管可以共享接地的源极(Source),从而大大减小存储单元的面积。为减小相变材料工艺对标准CMOS工艺器件的影响,相变材料被置于顶层金属(TM)和二层金属 (TM-1)之间,底电极 (bottomelectrode contact,BEC)一端连接二层金属,另一端连接相变电阻(GST)。

图2 存储单元版图结构

存储单元是相变存储器的核心,设计与制作时要考虑单元尺寸、操作电流的热效率、工艺稳定性与成品率等。BEC采用较为简单的柱状结构,以提高工艺稳定性和 成品率。在柱 状体内填 充侧壁,使BEC尽可能地细,以减小电极与GST的接触面积,提高操作电流的加热效率。选择电导率高、热导率低的材料作为BEC材料,可在提高加热效能的同时降低热耗散。另外,在GST材料外围增加包覆层材料,可进一步降低热耗散,有效减小发生相变所需电流。

NMOS管作为相变电阻R的选通开关,其上要流过相变所需的RESET电流,因而RESET电流的大小决定了NMOS管的尺寸。存储单元的尺寸由NMOS管的尺寸决定。通过优化制作工艺,增加驱动电流的热效 率,可减小RESET电流,从而减小NMOS开关管的尺寸、存储单元的尺寸以及芯片的功耗。尤其对大容量的相变存储器来说,存储阵列在整个芯片中所占面积的比例更大,减小存储单元尺寸可有效提高单元密度,减小整个芯片的面积,降低生产成本。

3 电路架构

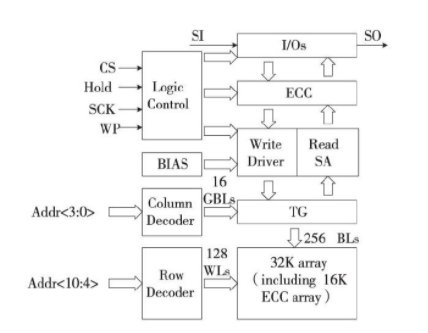

图3所示为16kb相变存储器芯片的电路架构框图。存储阵列容量为32kb,其中包含16kb的冗余模块,由纠错模块(ECC)控制选通。存储阵列的架构为128行字线,256列位线,通过传输门TG每16根位线连 接1根全局位 线 (global bit line,GBL),共16根全局位线。地址信号A<10∶4>译码128行字线,A<3∶0>译码16列全局位线,传输门TG将RESET或SET电流传输到位线中。由于RESET电流较大,传输门的尺寸也较大,引入了较大的寄生电容。当寄生电荷较多时,原本存"0"的单元可能会被误判为存"1",因而引入泄放电荷通道,在读写操作的空闲时间内,泄放其中的寄生电荷。

图3 PCRAM 芯片的电路框图

写驱动电路 (Write Driver)用于提供SET和RESET电流。由于RESET电流较大,在版图设计时需要考虑金属线的宽度是否足够宽,在电源、驱动电流以及地之间的整个通路上都要加宽金属线。

对于读出操作,每16根位线通过1根读操作位线(read bit line,RBL)与一个读 出放大器 (ReadSA)相连。读出放 大器采用 全对称的 差分拓扑 结构,两输入信号大小相同,方向相反,为相变单元电流与参考电流的差值[5].相较于输入信号为电压信号且两输入端阻抗不同的传统灵敏放大器,本文设计的读出放大器大大提升了抗干扰能力以及灵敏精度。同时,由于采用差分结构,两输入端信号的差值放大一倍,提升了读出速度。相变存储器的读电流很小,读操作时读电流经由RBL至阵列中的BL,不经过大尺寸传输门TG,减小了大寄生电容对读操作的影响,进一步提高了读出速度。

偏置电路(BIAS)可提供一些与电源和温度基本无关的电流或者电压,供其他电路使用。由于是模拟电路,在版图设计时加入了对模块以及关键信号通道的噪声屏蔽。纠错模块的引入使得每8位可纠错2位,可解决由 于工艺缺 陷等造成 的成品率(bit yield)下降问题。 逻辑控制 模块 (LogicControl)通过时钟SCK完成时序控制。芯片采用SPI接口,以1位的位宽串行输入输出数据。

4 版图设计

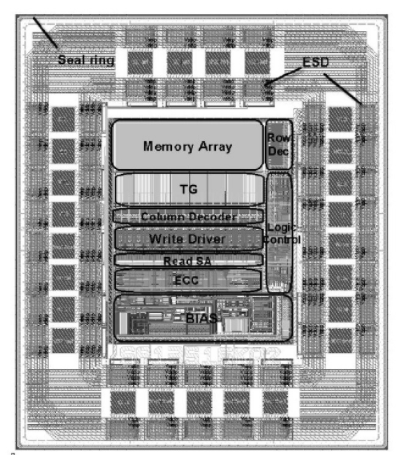

图4所示为16kb相变存储器芯片的整 体版图,芯片尺寸约为1.05mm×0.95mm.由于存储容量小,存储阵列的面积在整个芯片中占比不大。为保证RESET电流的供电能力,提高相变电阻的操作成功率,可以稍微加大存储单元中的NMOS开关管尺寸。为减小工艺误差对实际电路性能的影响,在每个存储阵列四周添加虚拟存储阵列,减小了边缘过刻蚀等工艺因素对实际有效电路的影响。

图4 芯片的版图

行译码器位于水平方向,译码器输出信号经大尺寸缓冲器加大驱动能力后,与存储模块中的字线相连。由于外 围电路采 用3.3 V NMOS管和PMOS管,而存储阵列采用1.2V NMOS管,为保证在过电压 (高于1.2 V的电压连 接在1.2 VNMOS管的栅极)驱动下NMOS管的寿命,以及考虑到1.2V NMOS管的电流能力,将驱动行译码器最后一级缓冲器的电压由3.3V降至2.5V.

传输门、列译码器、写驱动电路和读出放大器位于存储阵列的垂直方向,并与位线对齐。由于写驱动电路同时产生16路电流,而RESET电流为mA级别,写驱动中的电源线和地线应足够宽,以达到承载大电流的能力,同时电源线和地线的电阻应尽可能地小,以降低大电流流过时产生的压降。

由于读出放大器为全对称差分灵敏放大器,在版图设计时,要充分考虑器件及金属走线的对称和匹配。差分对电路采用交叉匹配的方式布置,金属走线的类型及形状尽可能一致。对于差分小信号来说,还要配置接地的屏蔽信号,以提高抗干扰能力。布线应尽可能短,以减小寄生电容,提高速度。

ECC电路位于读出放大器的下方。BIAS电路为模拟电路,置于内核电路的下方,与其他数字电路保持距离。数字电路的电源和地与模拟电路的电源和地分开布线,以减小串扰。为使布局紧凑,逻辑控制电路布置在行译码器下方的空白位置。

ESD保护结构用于吸收和耗散静电能量,预防静电失效。ESD结构对于芯片来说意义重大,合理的ESD结构可以保护内核电路不受外界静电侵害,从而可以在真实的环境中正常工作。ESD电路位于内核电路的四周,为预防闩锁效应,在内部电路和ESD结构之间添加了保护环。ESD结构的电源线和地线采用宽金属线布线(金属线的经验电阻值以1~2Ω为宜),并连接成独立的环状。不同于核心电路中的晶体管结构,ESD结构中的晶体管需要特殊处理,ESD晶体管漏极通孔到多晶硅栅的距离比普通晶体管大很多,而且还需去除漏/源边界的硅化层,这是为了增大PN结的串联电阻,多消耗部分ESD能量。在ESD静电泄露路径上的有源区以及金属连线均采用45°倒角,以预防尖角放电带来的早期雪崩击穿。ESD晶体管采用偶数栅结构,其边缘是源极而不是漏极,原因是为了避免不必要的寄生双极管效应。焊盘应放置在对应的ESD结构附近,以减小焊盘到ESD结构的连线电阻和电感,避免其对ESD正常工作产生干扰。

密封环的主要作用是减小划片时的应力对芯片的影响,防止芯片在划片时破碎。密封环由有源区、P+掺杂、各级通孔和金属构成。不同于其他电路中所使用的方形通孔,密封环中的通孔采用长条形,并围成一个环。这样芯片中每一层都有一个环形圈拦截,可给予芯片充分的机械和电气保护,并阻止水气从侧面断口进入芯片。同时密封环还连接地电位,增强了衬底接触,也屏蔽了来自芯片外的干扰,并且将切割所产生的静电通过接地的密封环就近释放,降低了对芯片的冲击影响。密封环需要距离内核电路一定的距离,并且密封环的四角要做较大的倒角处理,因为芯片的四角位置应力最大,此处不宜放置重要的器件。

5 测试结果

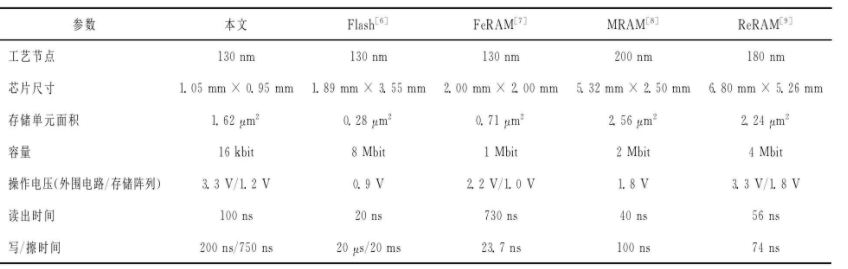

设计的16kb相变存储器芯片在中芯国际130nm CMOS工艺线上成功流片。芯片配置有两种方式,一种含有纠错单元ECC结构,一种屏蔽了ECC结构的功能,用以确认ECC结构的添加对芯片良率的提升所起的作用。芯片封装后的测试结果显示,芯片可正常进行读写擦操 作,经由ECC模块纠错后,成品率(bit yield)由86.0%上升至99.7%.在室温条件下,对封装后的相变存储器芯片进行了测试。表1提供了测试结果,并与主流的Flash存储器[6]以及新型 存储器FeRAM[7],MRAM[8],ReRAM[9]的相关参数做了对比。

表1 芯片测试结果及与 Flash,FeRAM,MRAM,ReRAM 的参数对比

6 总 结

本文介绍了采用中芯国际130nm CMOS工艺制作的16kb相变存储器芯片。该芯片使用了SPI接口,并含有ECC纠错模块。详细说明了1T1R存储单元的电路和版图结构,以及影响其尺寸的关键因素。存储单元是相变存储器的核心,提高存储单元的成品率以及减小存储单元的面积,对存储器来说意义重大。本文详细描述了提高单元操作电流热效率的方法。对电路的整体结构进行了描述,包括其主要构成模块及各模块的功能。读出放大器采用全对称的差分拓扑结构,大大提升了抗干扰能力、灵敏精度以及读出速度。详细描述了版图中各模块的布局、电源线和地线的布线方法,对称电路的匹配设计以及静电防护电路ESD和密封环的作用及版图设计注意事项。封 装后的芯 片测试结 果显示,在3.3V的操作电 压下,芯片的读 时间为100ns,Reset时间为200ns,Set时间为750ns.经ECC修复后的成品率(bit yield)获得显著提高,由86.0%提升至99.7%.