0 引 言

随着现代科学技术的发展,图像处理技术取得了巨大进步,在软硬件方面都取得了很多突破性成果。近些年来,图像处理技术被广泛应用在各个领域,其中也包括舰船等交通领域。由于这些应用领域对其精度和识别的速度都有一定要求,所以,高速图像处理技术得到了快速发展。随着 FPGA 相关技术的快速发展,其在高速图像处理领域中的应用也逐渐增多。FPGA 技术不仅可以提高图像处理的速度,同时也降低了功耗,给图像处理系统设计实现提供了更有效的方法[1].

1 中值滤波算法

中值滤波算法是 FPGA 图像处理方法中应用较为广泛的一种。中值滤波算法可以在滤除图像数据噪声的同时,较好地保护图像的边缘信息,方便图像的分析与处理。该计算是一种非线性图像处理方法,主要工作原理是通过把像素灰度按等级排列和计算,选取中间值作为输出。可用下式表示:g(x,y) = Meadian{ f(x - i,y - i) } ,i,j ∈ [0,N].

其中 f(x,y) 和 g(x,y) 分别为输入、输出的像素数据灰度值。中值滤波算法主要包括冒泡排序法和一般快速并行中值滤波算法。冒泡法的基本原理是对区域内的像素按灰度值按从小到大的顺序依次进行排序,将得到的中间值作为最终输出。但通过对冒泡法进行分析可以发现,对于 3 ×3 的像素区域,每执行完1 次运算,需要进行 36 次比较,而且相邻两点的计算过程中,会对其中的 6 个像素点进行 15 次重复的比较。这种重复计算不利于图像的实时处理。一般快速中值滤波算法引入了图像并行处理技术,先对选定区域内的像素进行分别排序,然后按照一定规则进行比较,最终得到中值,这样减小了算法的重复计算,一定程度提高了运算效率。

通过深入分析,可以算出一般快速中值滤波算法处理 3 × 3 像素区域时,仅需要 19 次比较计算,与冒泡排序法的计算次数相比减少了一半,节省许多时间,提高了图像处理的速度[2].

2 改进快速中值滤波算法

基于一般快速中值滤波方法,通过降低对相区域像素的重复比较次数,充分利用比较结果的思想,本文提出一种改进的快速中值滤波算法,即基于拓展像素处理区域。该算法主要优点在于能对图像数据进行多点的批量处理,一次对多组像素点进行排序。

通过选择一个 3 ×4 像素区域来改算法的实现过程。先选择一个 3 ×4 的像素区域,如表 1 所示。

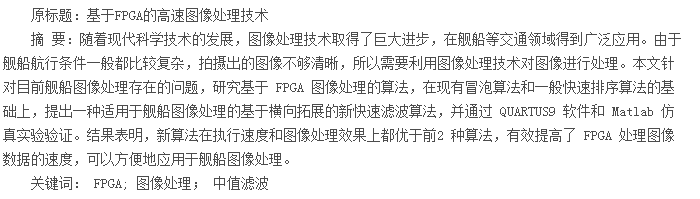

首先对像素区域进行编号,然后利用冒泡法进行排序,得到最小值、中间值和最大值,分别用A_MIN、A_MID 和 A_MAX 进行表示; 然后对 B 和 C这两列所得到的结果再进行交叉比较,可以得到MIN_OF_MIX 和 MAX_OF_MIN,即最大值相比取较小值,最小值相比取较大值,同时也对中间值进行比较得到 MAX_OF_MID 和 MIN_OF_MID; 最后把 A列和 D 列像素经过上面 2 次处理得到的结果再进行交叉比较,最终得到前 3 列的最小值里面的最大值MAX_ OF _ MIN1,最大值里面的最小值 MIN _ OF _MIX1.和中间值 MID_OF_MID1.同理,对后 3 列进行相同的操作,得到 MAX_OF_MIN2,MID_OF_MID2和 MIN_OF_MAX2.

通过以上步骤求出的像素点,根据分析可以确定最后所需要的中值像素点只可能在 MAX_OF_MIN1,MID_OF_MID1 和 MIN_OF_MAX1 中,所以最后对这 3 个像素点进行灰度值排序,得到最后确定的中值输出 MEDIAN1,即为前 3 列最后得到的中值输出。同理,对后 3 列也通过这种比较方法,得到后 3 列的中值输出 MEDIAN2.

再改进中值滤波算法中的最后 2 个步骤,只需要对图像数据进行冒泡排序,最后得到所需要中值的像素点 MEDIAN1 和 MEDIAN2,作为之前像素点 B2,C2 两个像素位置经滤波后得到的像素数据。

图 1 为本算法实现过程。

经过计算分析可知,改进快速中值滤波算法减少了重复排序操作,降低了比较次数。在 3 ×4 像素区域的排序过程中,改进快速中值滤波算法的比较次数为 29 次,比之前普通算法的 38 次减少了近30% .由此可看出,改进的快速中值滤具有较快的图像处理速度[3].

本文新提出的算法主要优势在于像素区域的选择上,与现有图像处理算法不同,本算法在 1 个周期执行完毕后可以对 2 个像素点进行滤波计算,而之前的算法只能对 1 个像素点进行滤波,这就使之前的窗口滑动速度由 1 个像素点提高到 2 个像素点,在每个周期的计算次数上降低了 50% 左右,从而可以极大地提高图像处理速度。

3 算法硬件实现和仿真

3. 1 滤波算法总体模块设计

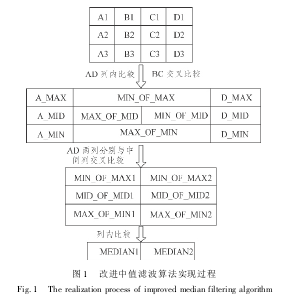

通过设计 2 个不同的模块生成模板和实现算法模块,来进行中值滤波算法在 FPGA 中的处理。在生成模板模块中,其主要功能是把所有等待处理的像素和相邻区域中的所有像素按照模板的形状进行去除,然后将处理后的数据传送给算法模块进行处理; 算法实现模块在接收到由生产模板模块处理过的数据后,对像素数据进行排序运算,然后求出中间值,作为所求像素点的最终中值滤波输出。

在生成模板模块中,需要用到 FIFO 存储器,FIFO 存储器可以通过采用 “先进先出” 的方式对需要保存的图像数据进行暂时性的存放。FIFO 存储器在数字信号处理系统中的应用非常广泛,可以作为传输数据的延迟线或者作为数据的缓冲储存器等[4].

在FPGA 芯片进行图像处理的过程中,一个 FIFO储存器用来存储1 行的像素数据,这样使模板的设计更加简单,也为之后的算法实现模块提供方便。由于要满足不同图像处理要求,需要对图像数据进行实时处理,所以在系统工作时,FIFO 的所有 RAM 一直都在不断刷新读取循环中,提高了图像处理速度。并且可以通过QUARTUSII 提供的模块来对 FIFO 进行设计。在本设计中,是通过LPM 红单元来对FIFO 模块进行设定。

3. 2 生成模板模块

图像数据在 FPGA 中视通过一行一行扫描,然后将数据进行串行输出,其中每传输 1 个数据仅需要 1个时钟周期,然后将串行的图像数据通过算法模块处理生成并行像素数据,所设计的 3 ×4 模板就是将串行数据转换为并行数据,数据在处理后,将得到的结果把原始像素数据的中间位置像素代替,然后传送给下一模块。最后通过不断的换行,完成整个完整幅图像的像素数据阵列的处理。为了将 3 ×3 阵列的所有像素并行输出,本文在 FIFO 存储器的设计中采用了2 个 linebuffer.每个 FIFO 的地址宽度就是选取的像素区域的宽度,这样可以保存整行像素数据。

行缓冲模块可先对 3 行像素数据进行处理,然后并行读取处理 3 行数据; 像素缓冲器用来将模板中串行的数据转换成并行数据输出。图 2 为生成模板模块的设计框图。

生成模板模块的工作流程为: 先把第 1 行像素数据传送进来,并将数据写入 linebuffer1 中; 然后在第 2 行像素数据传送进来时,先将 linebuffer1 里面的存储的第 1 行数据传送到 linebuffer2 中,再把刚传送进来的像素数据存入 linebuffer1 中。以此类推,最后将所有的像素数据并行输出给算法模块,实现生成模板的功能[5].

3. 3 中值滤波算法实现模块

本设计方案通过使用寄存器和比较器来实现改进的快速中值滤波算法。通过对比较排序过程的分析,对算法模块进行时序分段,对在一个时序段的比较器进行时钟同步。并将硬件结构设计成储存器-比较器-储存器的模式,这样设计的好处在于在改进快速中值滤波算法的执行过程中不会出现断点,也不会出现冗余的等待时间,从而更高效地实现流水处理功能。图 3 为此算法的硬件结构。

其中 COM1 模块为比较模块,可以对 3 个输入像素处理后再将排序号的 3 个像素输出到 COM2 模块,而 COM2 模块将接受到的数据进行处理后,通过 2 个比较器,将像素数据进行比较和排序,最终输出 1 个最大值或最小值,至此即完成了算法模块的设计。

3. 4 中值滤波算法 FPGA 仿真

前述已经完成模板模块和算法模块的设计。根据之前设计时所定义的输入接口与输出接口,通过将相同的接口信号对应起来,然后通过 QUARTUS环境下的 VERILOG HDL 中的实例化指令将其实现,就可以把所有模块进行有效连接,完成改进快速中值滤波模块设计。

下面通过 QUIARTUS 软件里面的 Simulator 对设计好的算法模块进行仿真,来验证其正确性。图 4 为最终输出的仿真波形。从最终输出结果可以发现,经过算法模块的处理,最终得到的滤波中值可以完整地输出,验证了本算法的正确性。

3. 5 仿真分析

经过对算法和 FPGA 硬件实现的仿真分析,本节将在Matlab 仿真环境下对算法进行可行性验证。通过使用冒泡算法、一般快速滤波算法和改进快速滤波算法3 种算法对灰度图像进行降噪滤波处理,对滤波效果进行对比分析,对处理的效果进行评价。

为充分验证 3 种方法在舰船图像处理上的效果,以 1 幅图片为例进行处理和验证。通过对灰度图像叠加噪声,然后将冒泡法、一般快速滤波法和改进快速滤波法分别对图像进行处理,再对比 3 种算法处理后的图像,如图 5 所示。经过对比图像可明显看出,本文提出的改进快速中值滤波算法可以达到相同的图像处理效果。为了能够定量判定新算法最终图像处理效果的好坏,采用对处理后的图像的信噪比进行对比,通过对叠加不同噪声的图片进行分析,分别对原图和处理后的图片的峰值信噪比进行对比分析。

对比结果如表 2 所示。通过表 2 可以发现,3种算法的峰值信噪比的差距很小,这些参数可以证明本文提出的新算法的滤波效果可以达到对舰船图像处理的要求,而且改进快速中值滤波算法在选取像素区域的偶数列中所处理的像素数据更多。

4 结 语

本文分析了传统的 FPGA 图像处理算法,对不同的中值滤波算法进行了对比和分析。重新提出改进的中值滤波算法,并经过 QUARTUS 软件仿真和MATLAB 数据分析,证明了提出的改进快速中值滤波算法不仅在图像处理速度上优于冒泡法和一般快速中值滤波法,而且在处理效果上也比前 2 种算法更好,可以方便的应用于拍摄图像质量不高的舰船图像处理领域。

参考文献:

[1] 刘昊。 高速图像处理平台的设计与实现[D]. 武汉: 武汉大学,2008.

[2] 万海军,何东健,徐尚中。 基于 FPGA 的图像中值滤波算法硬件实现[J]. 微计算机信息,2008,24(7) : 280 -282.